核心定位:解决“实验室跑通但产线大批量失效”的物理层问题

应广单片机(Padauk)凭借极致成本优势,成为消费电子、小家电、智能硬件量产首选方案。逐高电子作为应广科技正式授权代理商,长期深耕底层硬件开发与量产落地,依托原厂技术资源与芯片物理特性,为客户提供从选型、原理图设计、固件开发、PCB优化到产线调试的全流程产品开发解决方案。本文总结的10大开发深坑,均来自百万量级量产项目的真实踩坑经验,旨在帮助开发者从底层寄存器、半导体物理层面彻底规避风险,真正实现“一次开发、百万量产零退货”。

应广单片机(Padauk)是消费电子成本控制的极致。但极致意味着容错率低。在百万级量产背景下,任何一个对底层寄存器或物理特性的误读,都会导致 5% 甚至更高的退货率。

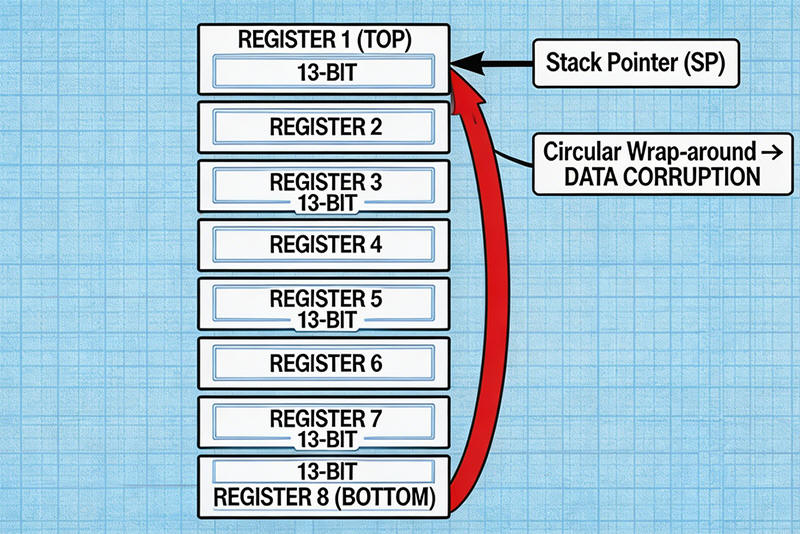

1. 硬件堆栈:LIFO 深度溢出与 SP 指针回绕

应广低端系列(如 PMS150/132)使用的是硬件固定位宽的堆栈寄存器阵列,而非 RAM 映射。深度被物理限制在 8 层。当程序调用超过 8 层时,堆栈指针会回绕至 0,覆盖最底层的返回地址。

long = long * int)时,会自动展开为多层子程序调用,这会隐式吃掉 2-3 层堆栈。.lst 汇编文件,手动复核所有 CALL 指令的绝对深度。2. FPPA 硬件切片:指令周期延展导致的时序协议解体

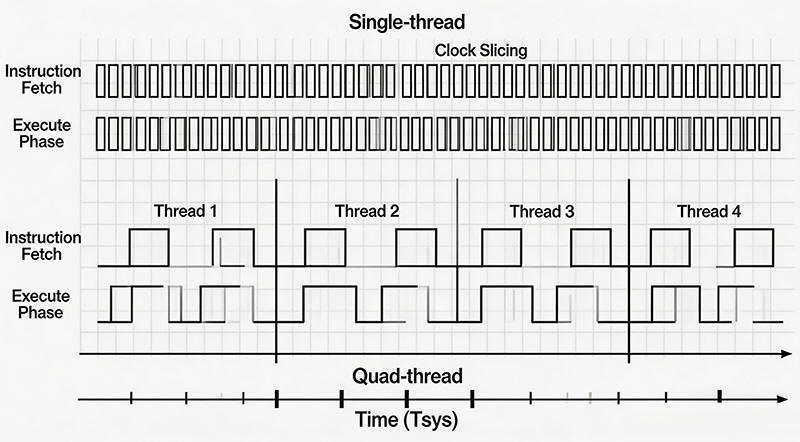

FPPA 通过相位切割(Phase Slicing)实现分时复用。当开启线程数 $N$ 时,每个线程的有效执行速度变为 $F_{sys} / N$。这不仅是速度变慢,而是物理脉宽的强制延展。

硬核细节:

如果你在线程 T1 模拟 UART 协议,在开启 4 线程模式下,原本一个 125ns 的 set1 指令物理耗时变为 500ns。更危险的是,多线程间由于共享总线,操作同一个 IO 寄存器会产生“读-改-写”竞争冲突。

精通方案: 时序敏感协议必须锁定在 T0 线程;在多线程并发时,涉及公共寄存器操作必须通过软件信号量或硬件标志位进行互斥。

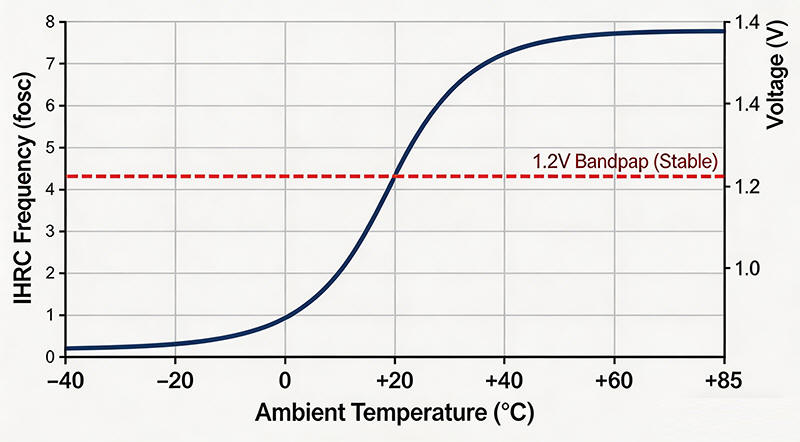

3. IRC 振荡器:能带隙(Bandgap)动态补偿频率漂移

IRC 的温漂(Temperature Drift)是非线性的。在量产中,不同批次的晶圆在 $-10^\circ C$ 下的漂移方向可能完全不同。依靠出厂的一次性校准(Calibration)无法覆盖全生命周期。

精通建议: 必须在程序主循环中加入基于 ADC 基准的 IHRC 微调,将波特率误差硬控在 ±1% 以内。

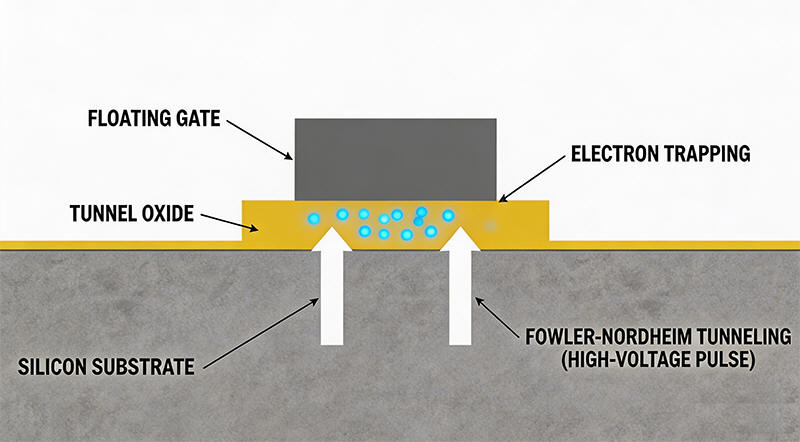

4. MTP 存储:Fowler-Nordheim 效应下的电子耗散陷阱

PFS 系列支持 100 次左右的擦写。其物理原理是通过高压脉冲隧道效应注入电荷。但应广的 MTP 没有 Flash 级别的纠错引擎,电荷在高温或多次擦写后会发生逃逸。

方案: 使用“多扇区轮询地址”算法分摊磨损,单点数据存储寿命可由 100 次扩充至 3200 次。

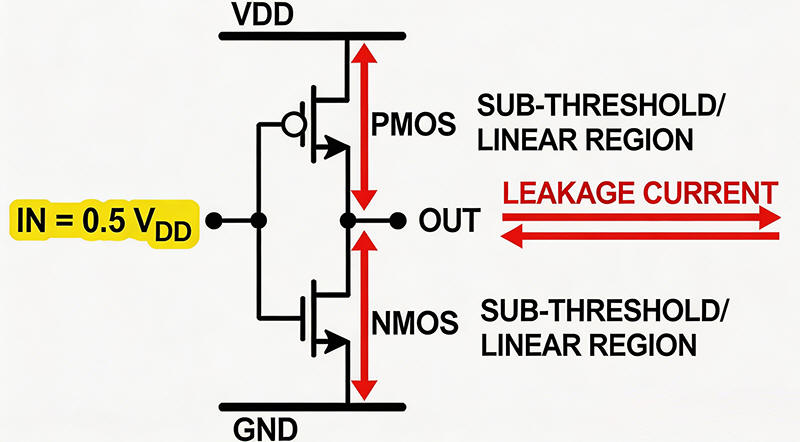

5. STOPSYS 漏电:CMOS 输入缓冲级的“穿越电流”

很多应广产品在睡眠模式下依然有几十 μA 漏电,导致电池耗尽。这通常是 IO 口设置为输入且悬空引起的亚阈值导通。

| 状态 | PAC 寄存器配置 | PA 寄存器配置 | 功耗表现 |

|---|---|---|---|

| 输入悬空 | 0x00 | N/A | 10-50uA (不稳定) |

| 正确睡眠配置 | 0xFF (输出) | 0x00 (拉低) | < 0.5uA |

6. 指令流水线:跨页跳转(Call Across Page)的时序崩溃

应广程序空间被分为不同的 Page(如 512 字一页)。当程序达到 0x3FF 边界时,跨页调用由于需要修改 PAGESEL 寄存器,若此时发生中断,返回时的页面状态位可能错乱。

避坑方案: 核心算法逻辑强制放在同一个 Page 内。在 IDE 中通过指令 #pragma page 或手动汇编定位地址,避免跨页跳转。

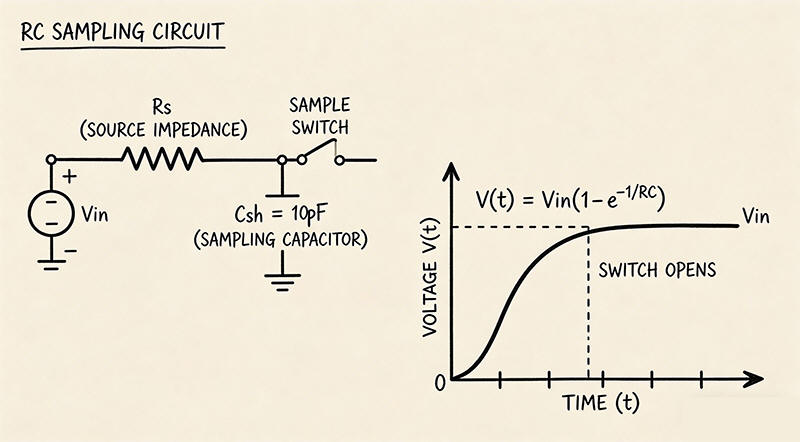

7. ADC 采样:采样保持(S&H)电荷转移误差

内部采样电容(约 10pF)在开关导通瞬间会吸走外部电路的电荷。若分压电阻大于 10KΩ,外部能量供应速度跟不上采样窗的闭合速度,读数会线性偏低。

工程对策: 在 IO 口并联 104 瓷片电容提供“电荷泵”;软件端开启 ADC 后,空跑 3 条 nop 指令以增加物理采样时间。

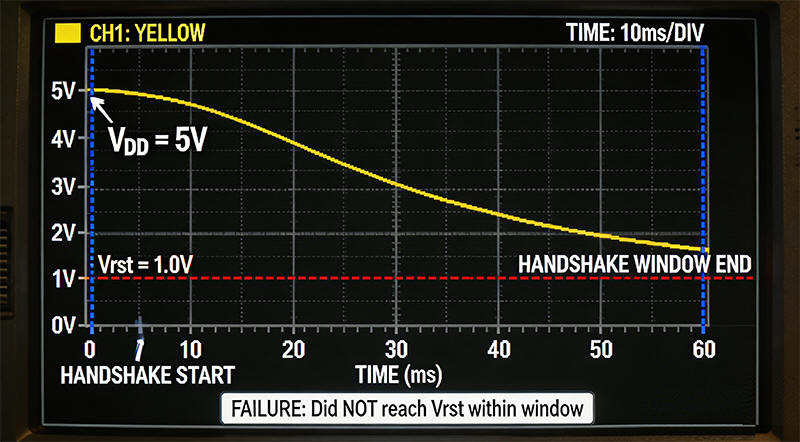

8. 烧录协议:VDD 掉电斜率与握手 FSM 失效

产线大批量烧写失败,往往是 PCB 板载大电容(>100uF)导致的。烧录器要求 VDD 在数毫秒内降至 0.5V 以下以重置状态机,但大电容维持了电压残留。

量产方案: 在烧录夹具上安装主动泄放电阻(1K 欧姆),确保电压跌落斜率符合应广 Writer 的握手时序要求。

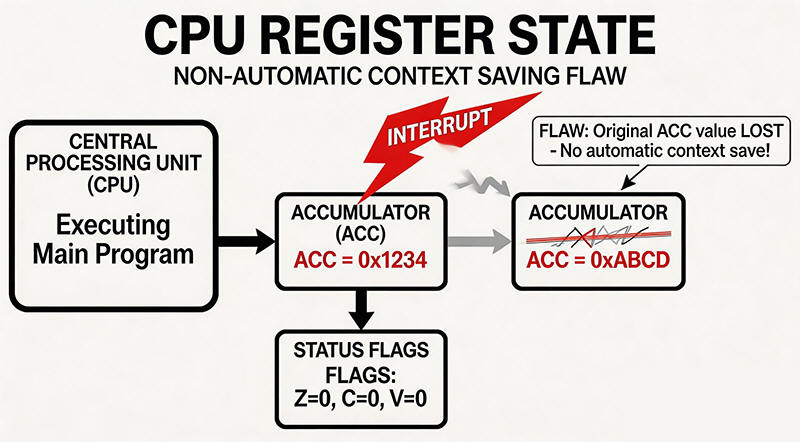

9. 中断原子性:ACC 与 STATUS 寄存器的“非自动保存”

应广 CPU 在进入中断时不自动压栈 ACC。如果你在中断函数里写了一句简单的 i++,它会悄悄改写累加器的值,导致主程序返回后的逻辑计算结果瞬间失效。

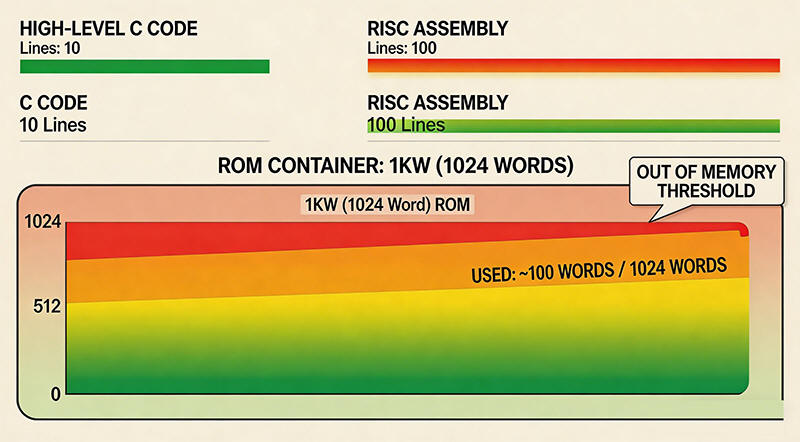

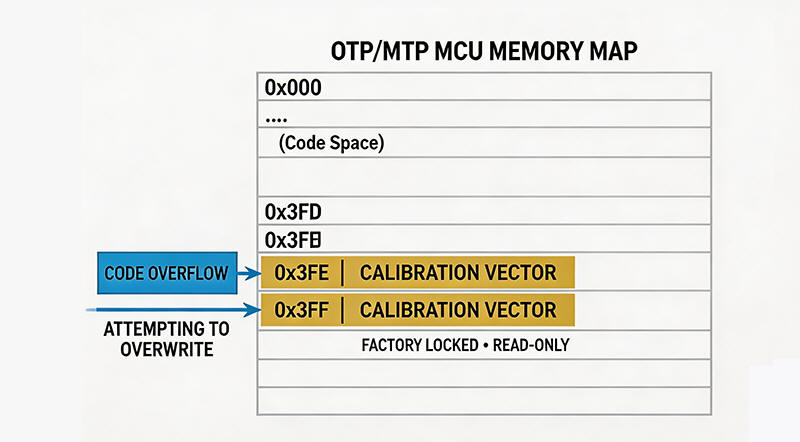

10. ROM 校准区:最后 1 字地址的代码溢出“自杀”

ROM 空间的最后地址(如 0x3FF)存放着晶圆出厂的 IHRC 校准值。如果你的代码因为逻辑膨胀写到了这个地址,烧录时会报错,或者覆盖掉该数据,导致芯片主频跑偏 20% 以上。

精通级建议: 在 IDE 编译设置中,将 ROM Limit 设置为 Max-2,永远留出物理冗余空间。交付 Hex 文件前,核对最后一行数据是否为全 0xFF 或合规校准占位符。